## Einführung

- 1. Vom Abakus zum PDA: Historische Entwicklung der Computer

- 2. Kleiner, schneller, billiger: Entwicklung der Mikroprozessoren

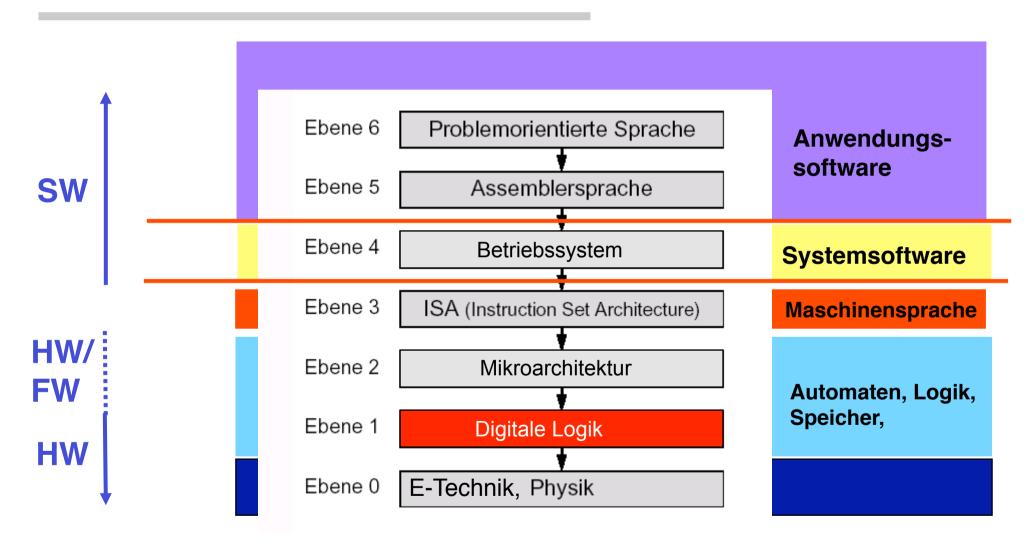

- 3. Schichtenmodell eines Computers

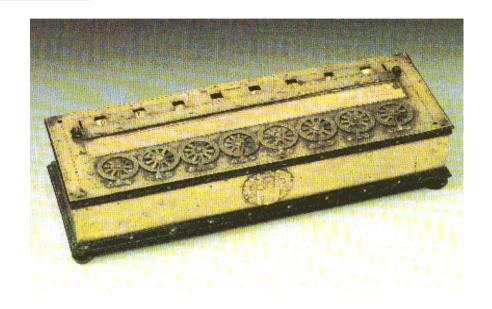

- 1642: **Pascaline**

- entwickelt von Blaise Pascal

- auf Zahnrädern basierend

- Addition von zwei bis zu8-stelligen Dezimalzahlen

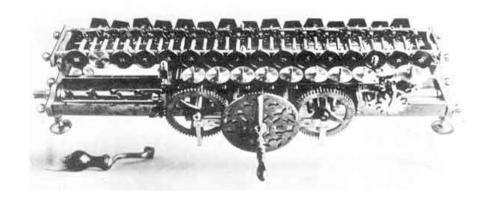

- 1673: "Stepped Reckoner"

- entwickelt von G.W. Leibniz

- neuartige Staffelwalze für Multiplikation, Division

#### Mechanische Rechenmaschinen

Staffelwalzenmaschine von J.H. Müller, 1784

Addiermaschine von C.G. Spalding, 1884

Rechenmaschine Curta von Curt Herzstark, 1938

#### Vom "Number Cruncher" zum Universalrechner

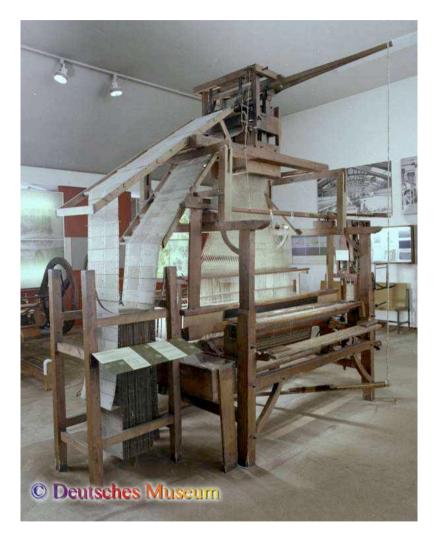

#### 1804: Lochkarte

entwickelt von Jacquard zur Steuerung eines Webstuhls

unterschiedliche Webmuster durch unterschiedlich gelochte Holzbrettchen

⇒ erstes

Read-Only Memory!

Joseph-Marie Jacquard (1752-1834). Das Bild wurde nach einem Kupferportrait mit Hilfe seiner Maschine gewebt.

http://www.deutsches-museum.de/ausstell/meister/web.htm

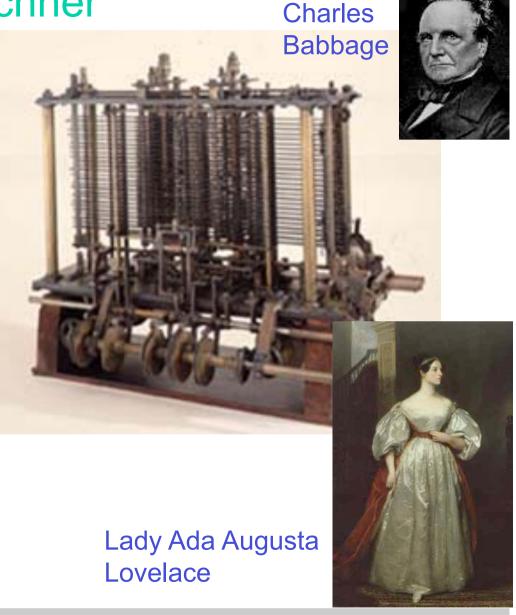

## Der erste Universalrechner

- 1830: "Analytic Engine"

- entwickelt von C. Babbage

- Steuerwerk, programmierbar mit Lochkarten

- Rechenwerk ("Mill")

- Speicher ("Store") für 1000

Dezimalzahlen aus 50 Stellen

- Ein-/Ausgabe mit Lochkarten

- Verzweigungen möglich

- Lady Ada Augusta Lovelace als erste Programmiererin

http://www.fourmilab.ch/babbage/sketch.html

## Die mathematische Grundlage des Digitalrechners

- 1854: Boolesche Algebra

- entwickelt von G. Boole

- binäre logische Operationen

- mathematische Basis für moderne Digitalrechner

'An Investigation of the Laws of Thought, on Which Are Founded the Mathematical Theories of Logic and Probabilities', 1854

Augustus de Morgan: Dass die symbolischen Prozesse der Algebra, ursprünglich zum Zweck numerischer Rechnungen erfunden, fähig sein sollten, jeden Akt des Denkens und der Logik zu liefern, dies hätte niemand geglaubt, bevor es in "Laws of Thought" bewiesen wurde.

#### Hollerith's Maschine

#### •1890: Tabelliermaschine

- -entwickelt von H. Hollerith zum schnellen Zählen und Sortieren (Volkszählung!)

- -Holleriths "*Tabulating Machine Company*" wurde 1924 zur Fa. IBM

Anwendung der Lochkartentechnik bei der 11. Volkszählung in der USA.

1880: 10. Volkszählung mit 500 Helfer, 7 Jahre Dauer 1890: 11. Volkszählung mit 50 Helfer, 4 Wochen Dauer

Hermann Hollerih 1860-1929

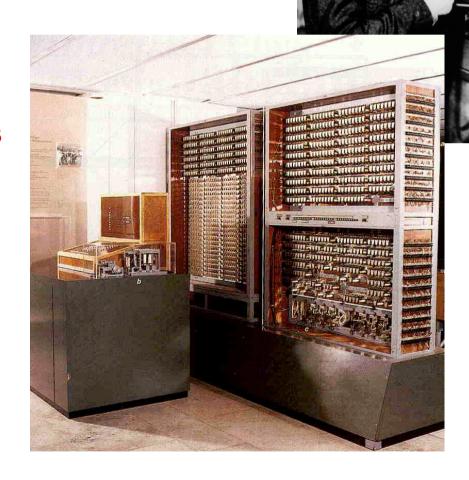

- 1941: Z3

- entwickelt von K. Zuse

- 10 Hertz Taktfrequenz

- basierend auf 2200 Relais

- 22-stellige Binärzahlen (im Gleitkomma-Format!)

- dezimale Ein-/Ausgabe

- Speicher mit 64 Worten

- Steuereinheit mit Sequenzer

- Addition in 3 Takten,

Multiplikation in 16 Takten

• 1945: Von-Neumann Architektur (Eckert/Mauchly, John von Neumann)

John von Neumann, left, with Robert Oppenheimer, Director of the Institute for Advanced Study from 1947-66

http://www.ias.edu/the-institute-letter/archive/03Winter/winter03.php

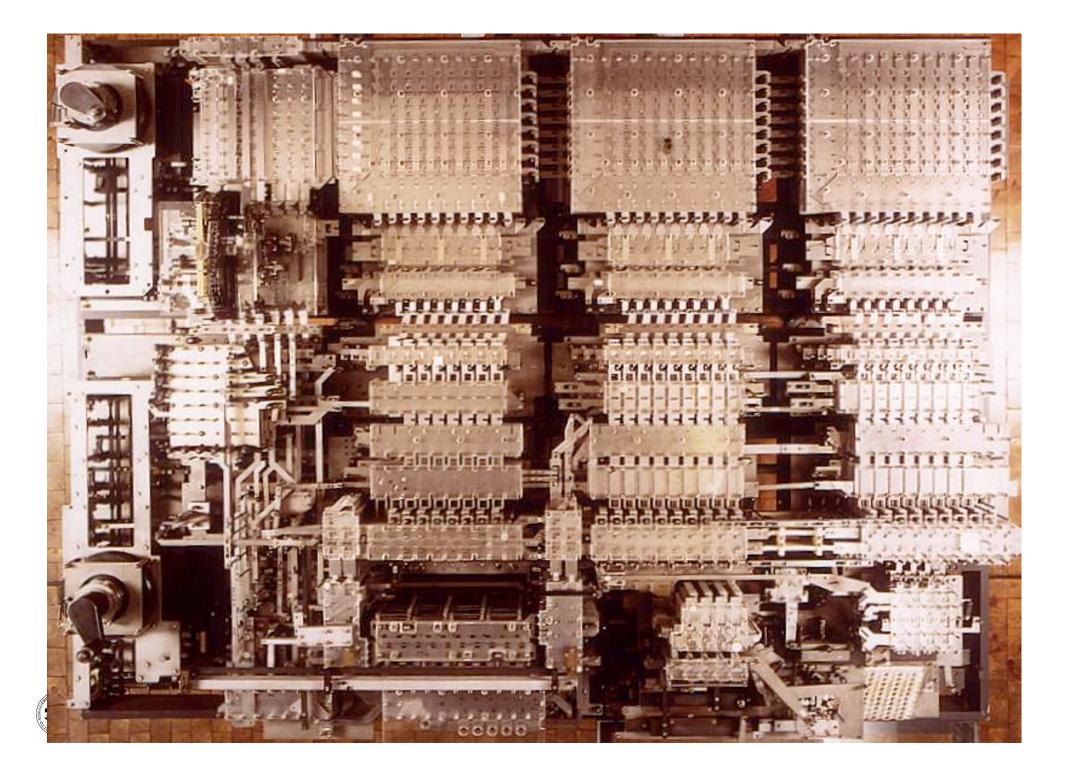

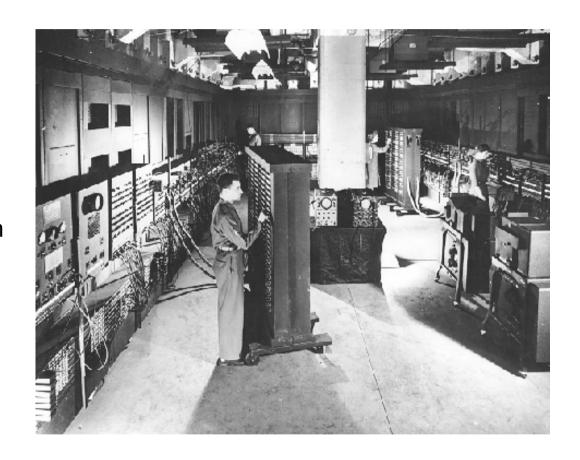

- 1946: ENIAC

- 18000 Röhren, 1500 Relais

- 130 m<sup>2</sup>, 30 Tonnen, 140 kW

- dezimale Kodierung

- ca. 5000 Additionen je Sek.

- 20 Akkumulatoren, 1 Multiplizierer, 3 Funktionstabellen

- programmiert durch Kabel-Verbindungen

- E/A mittels Lochkarten

- gebaut für ballistische Berechnungen

Gloria Gorden and Ester Gerston at work on the ENIAC

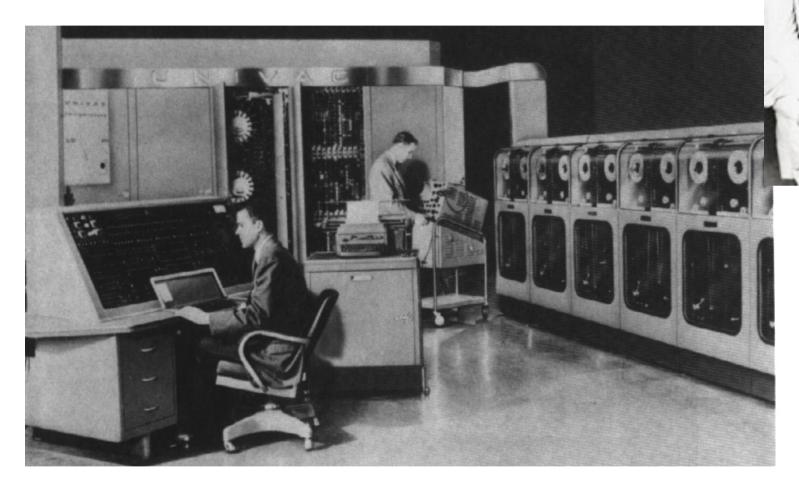

#### **Univac I**

J. Presper Eckert an der Schlüsselerfindung der UNIVAC, dem Quecksilberlaufzeitspeicher. (HNI)

Remington Rand 1951, entworfen von J. Presper Eckert und John Mauchly

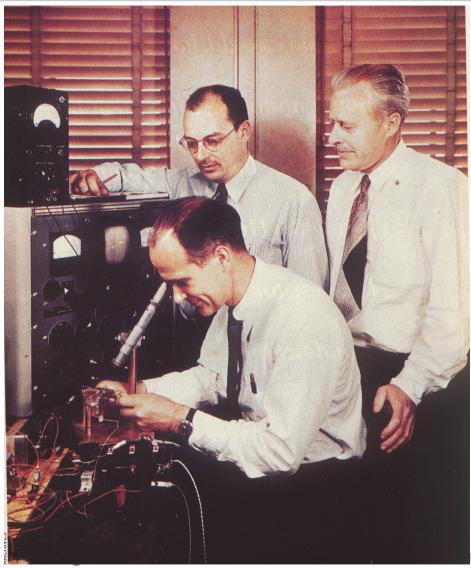

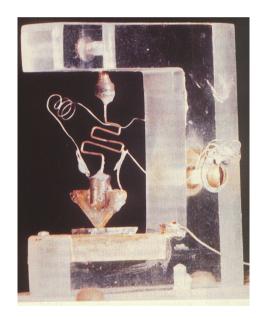

## Grundlage für heutige Rechner: Halbleiter

1948 Walter H. Brattain John Bardeen

**William Shockley**

**Der Ur-Transistor**

Wintersemester 09/10

#### PDP-8

- 1961: PDP-1

- gebaut von DEC

- auf Transistortechnik basiert

- magnetischer Kernspeicher für 4096 18-Bit Worte

- 200 kHz Taktfrequenz

- CRT, 512 x 512 Pixel Grafik

- ⇒ erster Minicomputer

Es folgten: PDP-8 mit Omnibus (erstes **Bussystem**, 1965), PDP-11 (erster **16-Bit** Rechner, 1970)

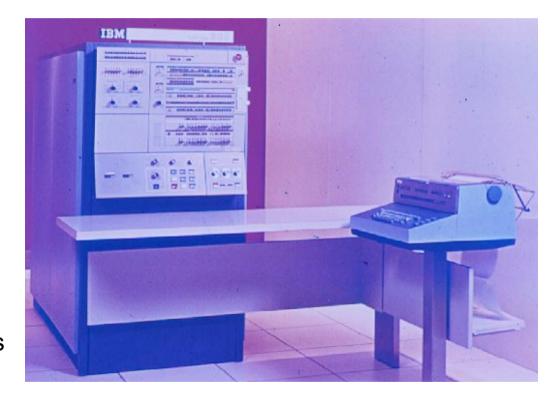

## Hermann Hollerith's Enkel

- 1965: IBM System/360

- erste Rechnerfamilie mit gleichem Instruktionssatz

- Mehrprogrammbetrieb

- Mikroprogammierung

- Verwendung von integrierten Schaltkreisen (ICs)

- 32-Bit Worte

- 16 Mbyte Adreßraum

- typischer Großrechner (auch als "Mainframe" bezeichnet)

- Weitere Meilensteine der Computer-Hardware:

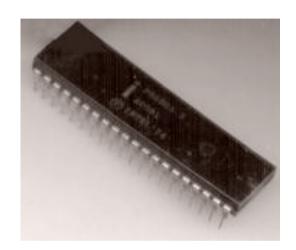

- 1971: erster Mikroprozessor auf dem Markt (Intel 4004)

- 1976: Cray-1 (erster Vektorrechner)

- 1985: MIPS (erster kommerzieller RISC-Mikroprozessor)

- 1987: Connection Machine (erster massiv paralleler Rechner mit 65536 Prozessoren)

- 1992: DEC Alpha 21064 (erster RISC-Mikroprozessor mit 64-Bit CPU)

- 1997: Supercomputer ASCI Red liefert eine Rechenleistung von mehr als 1 TFlops

- 2000: erster Mikroprozessor mit 1 GHz Taktfrequenz

#### Entwicklung der Mikroprozessoren

- 1974: Intel 8080 (erste universelle

8-Bit CPU auf einem Chip)

- 1978: Intel 8086 (erste 16-Bit CPU auf einem Chip)

- 1979: Motorola 68000 mit 32-Bit interner Architektur

- 1981: Einführung des IBM PC

- 1985: Intel 80386 (32-Bit CPU)

- 1989: Intel 80486 (Cache + FPU auf dem Chip)

- 1993: Intel Pentium (zwei Pipelines)

- 1995: Intel Pentium Pro (bis zu fünf Operationen gleichzeitig)

- 2002: Intel Pentium 4 (Trace-Cache)

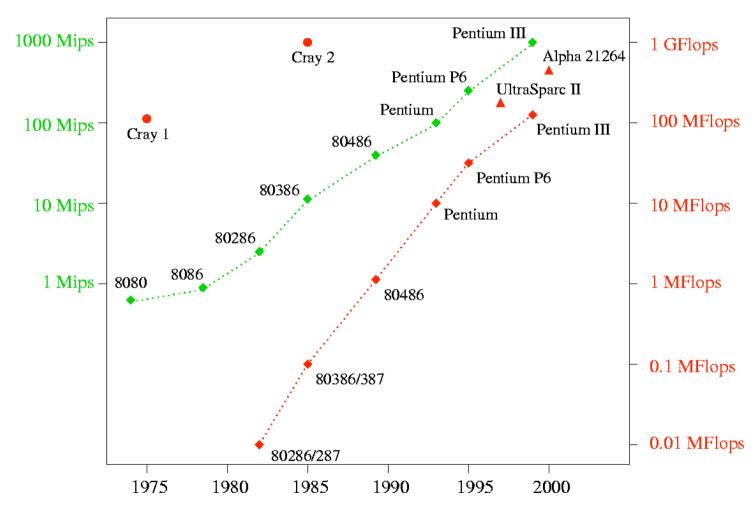

## Entwicklung der Mikroprozessoren

Leistungssteigerung 1975-2000:

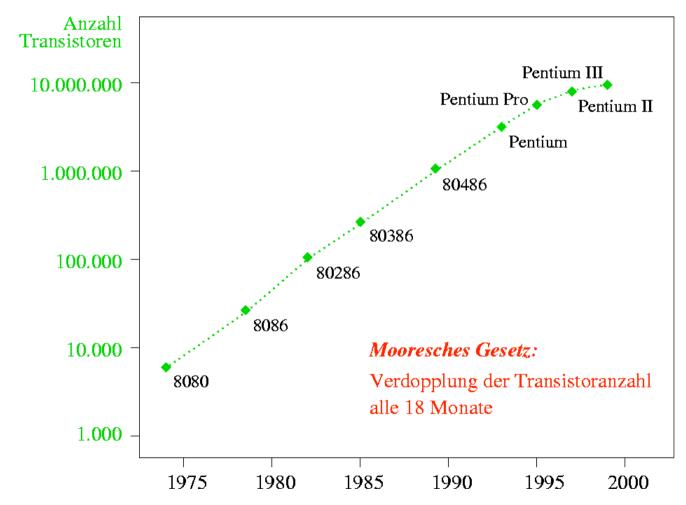

## 2 Entwicklung der Mikroprozessoren (3)

Komplexitätssteigerung 1975-2000:

## Top 10 der Supercomputer November 2005 (nach Linpack-Benchmark; Rang in Klammern: Juni 2005)

| Rang    | Hersteller | Rechner                                           | Standort 1                                       | Rechenleistung<br>(Gigaflops) |

|---------|------------|---------------------------------------------------|--------------------------------------------------|-------------------------------|

| 1 (1)   | IBM        | Blue Gene/L, PPC440, 0,7 GHz                      | Lawrence Livermore<br>National Lab, USA          | 280 600                       |

| 2 (2)   | IBM        | Blue Gene, PPC440, 0,7 GHz                        | IBM Thomas J. Watson<br>Research Center, USA     | 91 290                        |

| 3 (13)  | IBM        | Asci Purple, P-Series 575, 1,9 GHz                | Lawrence Livermore<br>National Lab, USA          | 63 390                        |

| 4 (3)   | SGI        | Columbia, Altix,<br>Itanium 2, 1,5 GHz            | NASA Ames Research<br>Center, Moffett Field, USA | 51 870                        |

| 5 (-)   | Dell       | Thunderbird, Poweredge 1850, 3,66 GHz             | Sandia National Labs,<br>Albuquerque, USA        | 38 270                        |

| 6 (10)  | Cray       | Red Storm, XT3,<br>Opteron, 2 Gigahertz           | Sandia National Labs,<br>Albuquerque, USA        | 36 190                        |

| 7 (4)   | NEC        | Earth Simulator,<br>SX6 Vektor                    | Earth Simulator Center,<br>Yokohama, Japan       | 35 860                        |

| 8 (5)   | IBM        | Mare Nostrum, JS20<br>Cluster, PPC970,<br>2,2 GHz | Barcelona Supercomputer<br>Center, Spanien       | 27 910                        |

| 9 (8)   | IBM        | Blue Gene, PPC440, 0,7 GHz                        | Universität Groningen,<br>Niederlande            | 27 450                        |

| 10 (11) | Cray       | XT3, 2,46 GHz                                     | Oak Ridge National Lab, I                        | JSA 20 527                    |

Quelle: Jack Dongarra, Hans Werner Meuer, Horst Simon, Erich Strohmaier COMPUTER ZEITUNG 46/2005

#### rechner

netween Earth Simulators Result (upper) on (lower)

Simulation

Observation

Processors per node

#### Peak Performance

Per node

Per processor

Main Memory

Per node

#### Juni 09, Hamburg

#### http://www.supercomp.de/isc09/News-Press/For-Journalists/Press-Releases

Holding onto the No. 1 spot with 1.105 (1,105 in deutscher Notation: 1,105 x 10\*\*15!!) petaflops (quadrillions of floating point operations per second) is the Roadrunner system at DOE's Los Alamos National Laboratory (LANL) which was built by IBM and in June 2008 became the first system ever to break the petaflop/s Linpack barrier. It still is one of the most energy efficient systems on the TOP500.

Maintaining its hold on second place is the **Cray XT5 Jaguar** system installed at the DOE's Oak Ridge National Laboratory. Jaguar reached **1.059 petaflop/s** shortly after its installation but due to its heavy workload no further measurements were possible.

#### Wo werden Rechner eingesetzt?

#### Wo werden Rechner eingesetzt?

- Fünf Computer, 2 verschiedene Typen jeder Computer besitzt interne Redundanz

- Vier unterschiedliche Softwaretypen von 2 verschiedenen Lieferanten.

- 3 Kabelstränge B, G, Y, separat durch das Flugzeug geführt.

- Mehrere Aktuatoren kontrollieren eine physische Steueroberfläche.

- Mehrere Computer kontrollieren einen Aktuator.

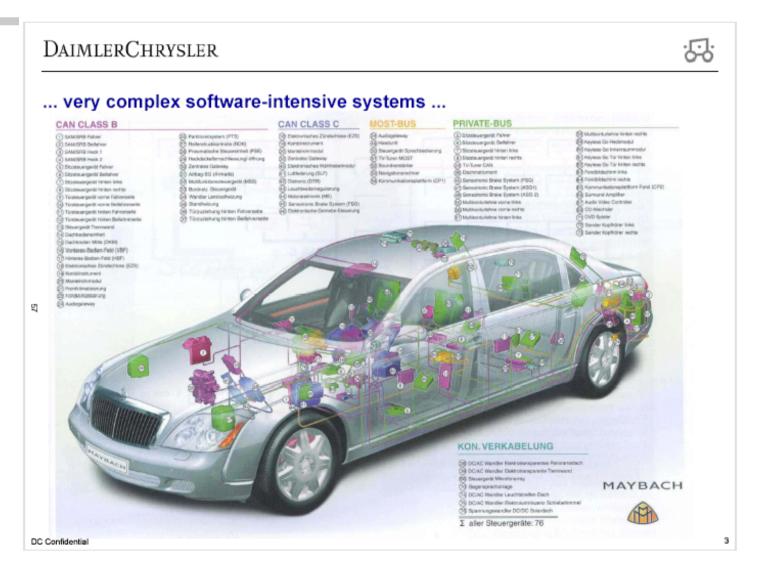

### Wo werden Rechner eingesetzt?

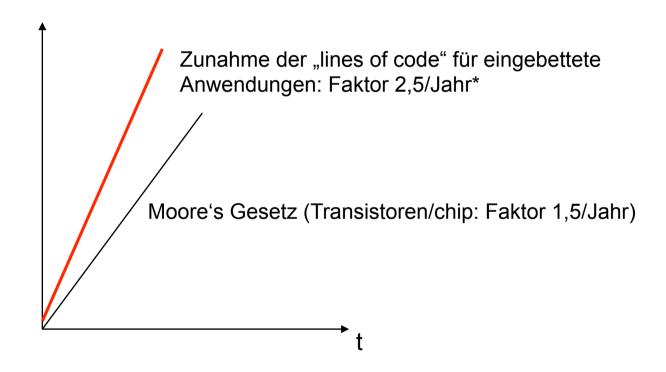

99% aller Prozessoren werden in eingebetteten Systemen eingesetzt

\*Quelle: Vortrag R. Hartenstein anläßlich: "Computing Frontiers", 2004

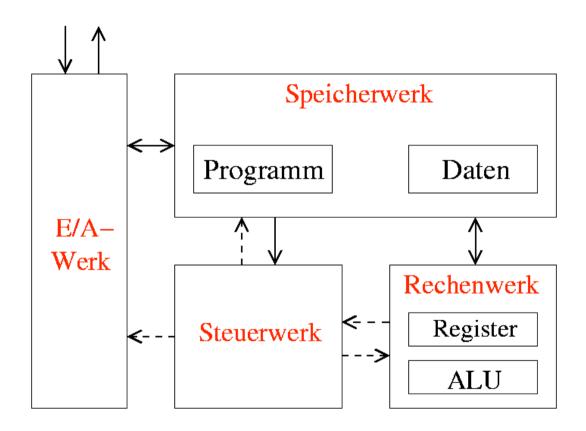

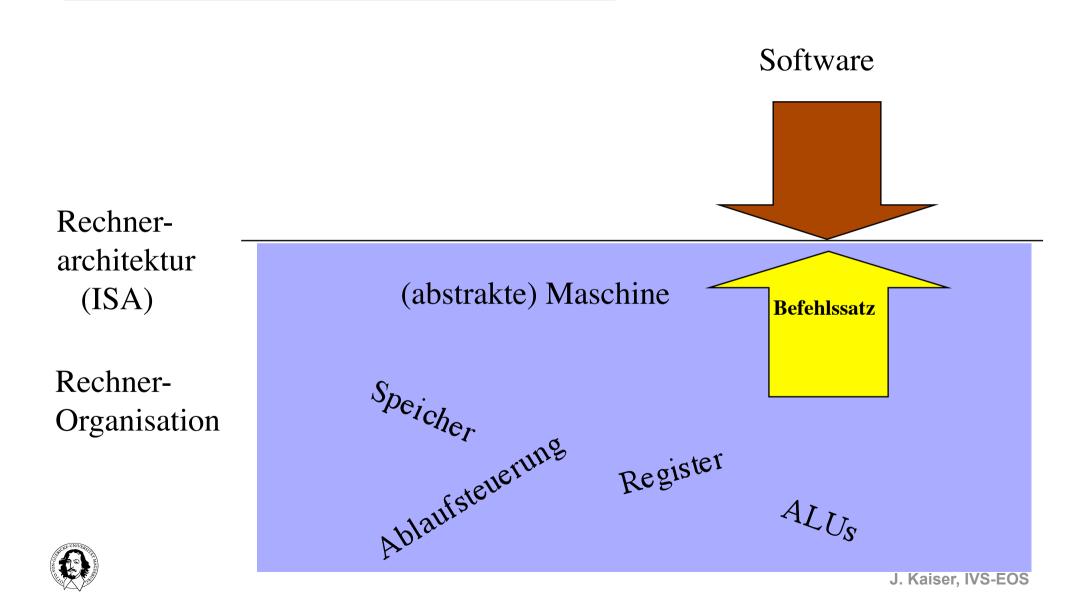

## Komponenten eines Rechners und ihr Zusammenwirken

## Die Hardware/Software Schittstelle

Übersetzer (Compiler)

**Assemblerprogramm**

Übersetzer (Assembler)

Maschinenprogramm

int fact (int n)

{

f = 1;

i = 1;

while (i++ < n)

f = f \* i;

return (f);

}</pre>

LDB -1, X **CMPB** ,X **BGE** OUT **INCB** STB -1, X LDA -2 ,X MUL STB -2 ,X REPEAT BRA

0100110 01101111 01010101 0000100 01010110 01000010 0011111 11000110 11111000 0000000 00100100 01110001

Prozessor-

abhängig

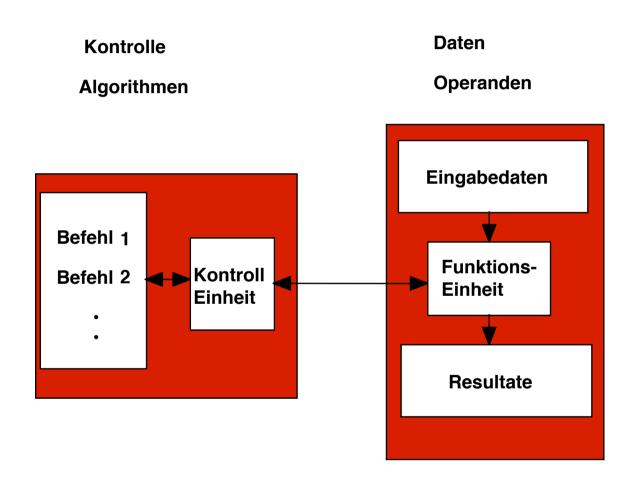

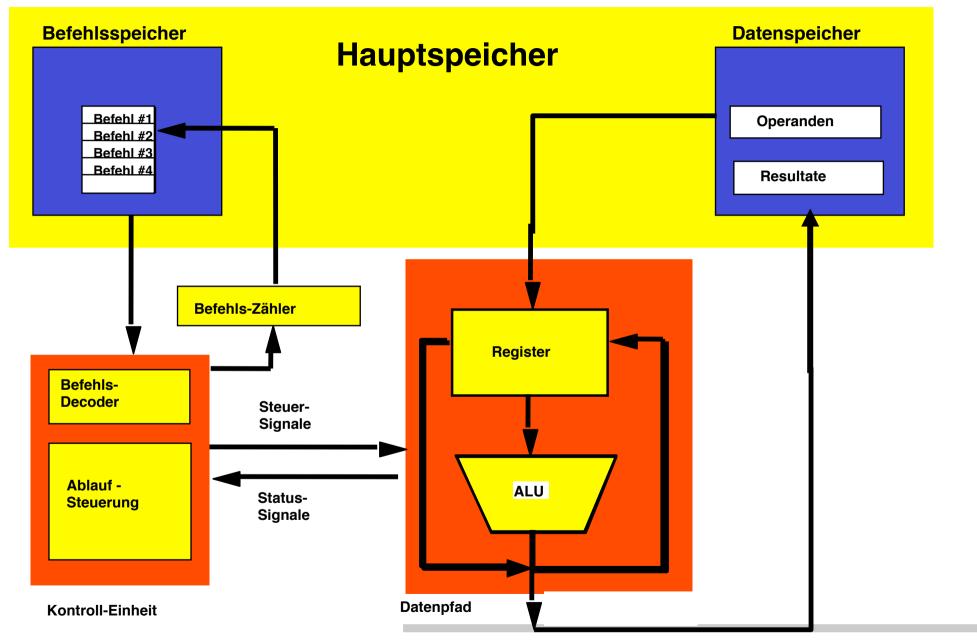

## **Grundlegende Struktur einer CPU (Central Processing Unit)**

## Das Prinzip des universellen Interpretierers

#### Prinzipien des "Stored Program Computer" Ansatzes:

- 1.) Instruktionen sind als Binärzahlen codiert

- 2.) Die Verwendung von Schreib/Lesespeichern für Programme

#### Komponenten einer "Central Processing Unit" (CPU)

# Schichtenmodell eines Rechners

Ebene der Rechner-Architektur (ISA)

S, X **TFR LEAS** -2, S **BSR FACT PULS** Α 2,S **LEAS**

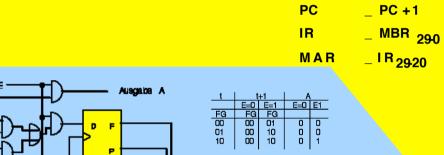

MBR

Memory

**MBR**

MAR

Register-**Transfer Ebene**

Ebene der Logischen Komponenten

PC IR Α Z ALU

\_ M [in str]

Ebene der Elektronischen Komponenten

| Ebene der<br>Rechner-<br>Architektur       | Rechner- Architektur  Vollständige Rechner |                |                     | Strukturen: CPUs, Coprozessoren, dezidierte Funkltionseinheiten, Attached Processors, (IUs, FPUs, MMUs, Graphik-Beschleuniger)  Komponenten: Instruktionssätze, Kontrolle der Zusammenarbeit |

|--------------------------------------------|--------------------------------------------|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (ISA, ISP)                                 |                                            |                |                     | Strukturen: Instruktionssätze  Komponenten: Speicherzustand, Prozessorzustand, Adressberechnung, Befehlsdecodierung, Befehlsausführung, Synchronisation paralleler Funktionseinheiten        |

|                                            | Register-<br>Transfer-<br>Ebene            | Steuerung      | Mikro-<br>progamm   | Strukturen: Mikroroutinen, Mikroprogramme  Komponenten: Mikroprogr. Steuerungen, Mikroprogr. Speicher                                                                                        |

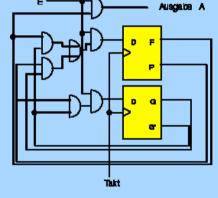

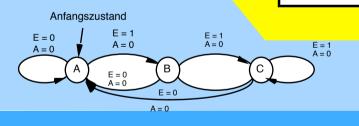

|                                            |                                            |                | Festver-<br>drahtet | Strukturen: Ablaufsteuerungen (Sequencer) Komponenten: Sequentielle Maschinen                                                                                                                |

| Ebene der<br>Logischen<br>Komponenten      |                                            | Datenpfad      |                     | Strukturen: ArithmLogische Einheiten (ALU),<br>Registersätze<br>Komponenten: Register, Funktionsgeneratoren                                                                                  |

| ·                                          | Schaltkreis-<br>Ebene                      | Sequentiell    |                     | Strukturen: Register, Zähler, Funktionsgeneratoren Komponenten: Flip-Flops, Latches, Verzögerungselemente                                                                                    |

|                                            |                                            | Kombinatorisch |                     | Strukturen: Encoder, Decoder, elementare arithmetische und logische Funktionseinheiten Komponenten: logische Gatter                                                                          |

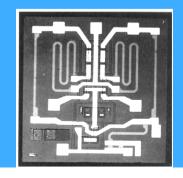

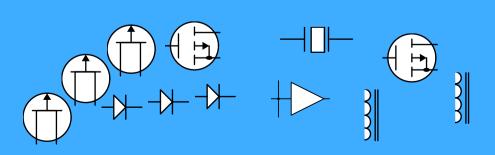

| Ebene der<br>Elektronischen<br>Komponenten |                                            |                |                     | Strukturen: Verstärker, Verzögerungsglieder, Schalter  Komponenten: Widerstände, Kondensatoren, Transistoren,                                                                                |

## Schichtenmodell eines Computers